什么是傳輸線阻抗

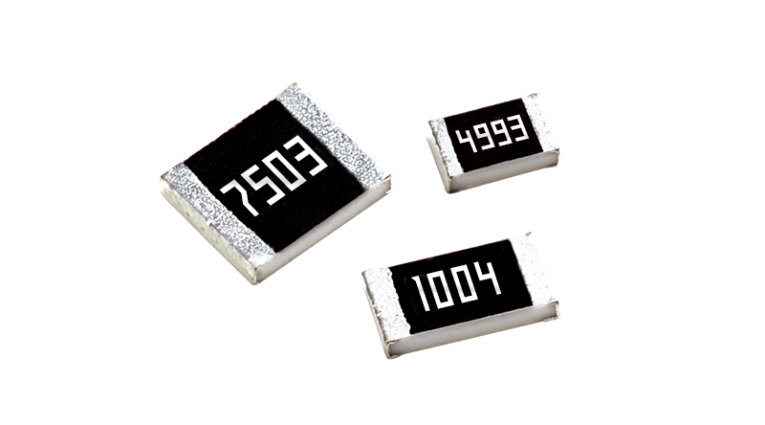

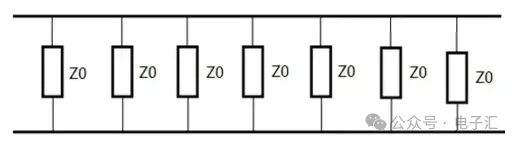

我們知道傳輸線理想簡化模型如下圖所示,這似乎跟導(dǎo)線電阻沒半毛錢關(guān)系?從模型來看,的確跟導(dǎo)線電阻沒有關(guān)系,但是該結(jié)構(gòu)整體所體現(xiàn)出來對信號邊沿的作用更像是一個電阻(厚膜貼片電阻/插件電阻):呈現(xiàn)串聯(lián)電阻(阻性)和延時的效果?

傳輸線理想模型

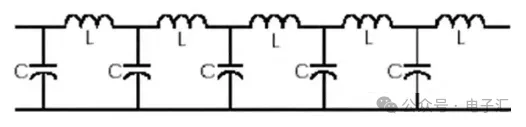

如上圖為無損傳輸線模型,以及在信號傳輸過程中的電流完整的流動過程,我們用L和C來描述傳輸線的回路電感和電容;

1. L指的是回路電感,這是一個等效電感:不是信號路徑的局部電感,而是信號路徑與回流路徑構(gòu)成的回路電感;所以該電感跟回流路徑強相關(guān)?舉個例子:當(dāng)傳輸線信號路徑不變,而回流路徑不連續(xù)時(例如:信號線的參考GND層被分割,回流路徑就要繞遠(yuǎn)路),傳輸線的電感就會增大;

如之前所述傳輸線電感展開如下圖:Lloop = L1+L2-2*L12;

2. C在如上拓?fù)渲?指的是信號路徑相對于回流路徑之間的電容?

舉個例子:信號線與回流地之間的板間電容,其間距是PCB層間距,介電常數(shù)是FR-4材料的參數(shù)?

如此,我們知道無損傳輸線的阻抗模型等效為:很多組串聯(lián)在信號路徑上的L和并聯(lián)在信號路徑與回流路徑之間的C組成;而且電流是從信號路徑到回流路徑的方向,由此得出:傳輸線的阻抗可以等效為搭接在信號路徑與回流路徑的一個電阻(并聯(lián)電阻),如下圖所示?搞錯沒得?這跟之前看到過的傳輸線等效模型完全不一樣啊,明明記得之前看到的特征阻抗似乎是“串”在“導(dǎo)線”上的誒?

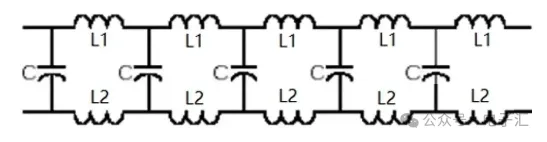

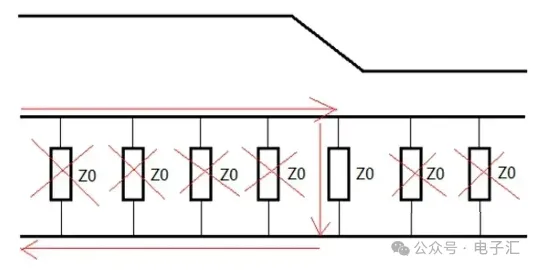

的確,這個并聯(lián)的模型似乎有致命問題:如上圖所示,如果傳輸線的阻抗是搭在信號路徑與回流路徑之間的電阻,那么這么多電阻并聯(lián)后應(yīng)該是Z0/n而不是Z0,假如有一根無線長的導(dǎo)線,那么特征阻抗就為0了么?這違反了常識和電路的基本原理啊?

撓了半天的頭,還是先回到傳輸線的定義來看看:信號在傳播過程中只有信號前沿的那部分導(dǎo)線才能看成是傳輸線?原來如此!如下圖所示,在信號跳變的左側(cè)是高電平(例如3.3V),右側(cè)是低電平(0V),信號路徑與回流路徑上的電壓差保持不變,沒有發(fā)生充放電的動作,所以這些地方阻抗是無窮大(導(dǎo)線上的信號是固定電平,則信號路徑和回流路徑之間電壓不會變化,此時電容不會進行充放電,所以電流I = 0;而Z =U/I = ∞,相當(dāng)于斷開);只有處于信號跳變處的信號路徑與返回路徑之間進行著充放電的動作,電容和電感才有了用武之地,成為傳輸線的“阻抗”:Z0?如下圖所示?

那結(jié)論就出來了:傳輸線的阻抗是信號前沿(跳變)處所受到的阻抗,它是一個瞬時的阻抗?所以傳輸線阻抗也可以看成串接在信號路徑上的一個電阻?

好,我們現(xiàn)在來總結(jié)傳輸線阻抗的描述:傳輸線阻抗是信號在傳輸過程中,信號前沿所受到的信號路徑與回流路徑之間瞬時阻抗?

如果傳輸線的瞬時阻抗在整條“導(dǎo)線”上都保持恒定(傳輸線瞬時阻抗保持一致),那么我們稱之為:傳輸線的特征阻抗?傳輸線特征阻抗的特點是:它只與介質(zhì)材料?傳輸線結(jié)構(gòu)相關(guān),與傳輸線長度無關(guān)?因為無論你在后面再加多長的50Ω阻抗的傳輸線,也只是向后再并聯(lián)了50Ω阻抗,在跳變沿路過這段“導(dǎo)線”的瞬間才有用?所以阻抗是疊加不上去的?